Sapphire Radeon X1900XT

Pag. 5 - Caratteristiche (3)

Profondo rinnovamento l’ha subito il controller di memoria, da sempre uno dei punti di forza della tecnologia Radeon. Fino alla passanta generazione, il controller di memoria (con bus a 128 o 256bit) faceva da accentratore dei flussi di dati che viaggiavano da e verso la memoria on-board. Da qui si andava, poi, ad indirizzare i dati verso i 2 o 4 controller secondari a 64bit. Ma in questo modo le latenze che si vanno a creare (quando un client aspetta delle informazioni che un altro sta per ricevere) sono insopportabili.

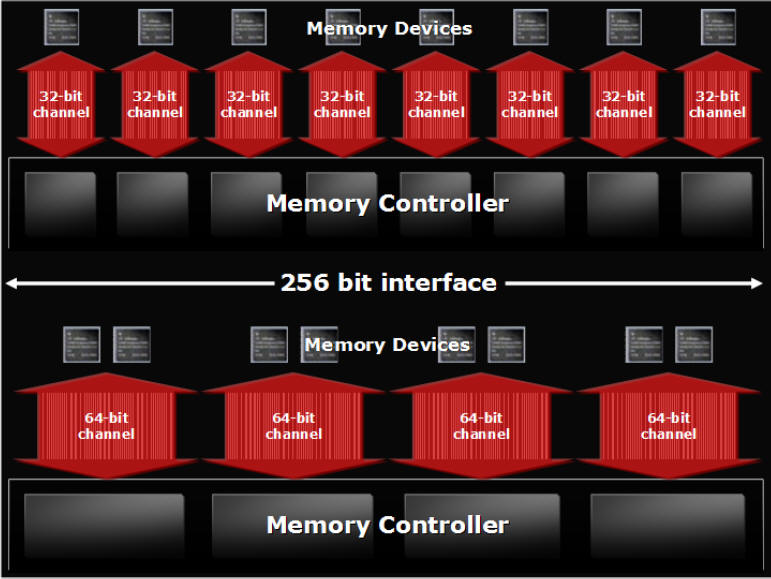

Il primo elemento su cui Ati ha lavorato è la granularità del controllo della memoria, cioè la possibilità di dividere il bus in canali multipli ora da 32bit invece che da 64 come in passato: il risultato è una maggiore efficienza per via del fatto che ora anche richieste di memoria meno esose non tengono occupato un canale intero.

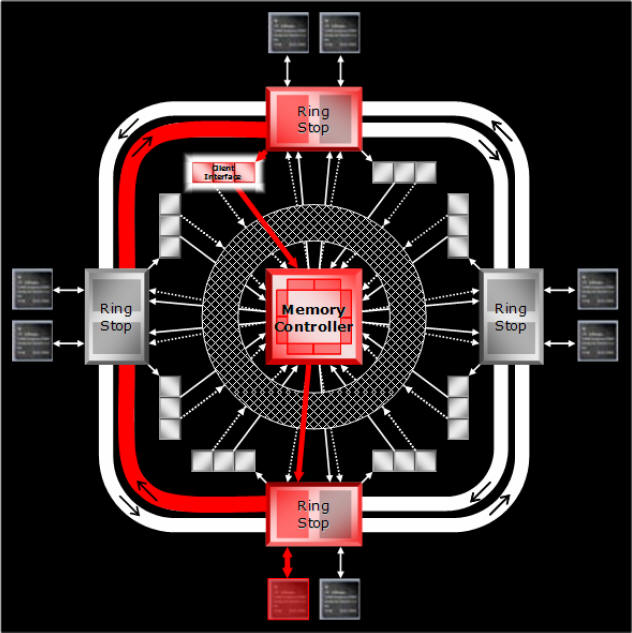

Vista anche la complessità sempre maggiore del controller di memoria e visti i continui accessi alla Ram e l'impossibilità di avere un segnale elettrico stabile per poter viaggiare a frequenze molto elevate con la GDDR3, Ati ha deciso di adottare un nuovo approccio: creare un bus ad anello o Ring bus.

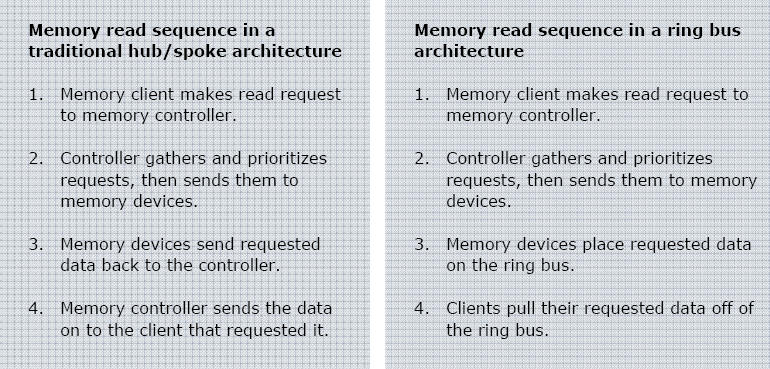

Ciò che cambia ora non è tanto il modo di fare una richiesta, quanto quello di riceverlo, ci spieghiamo meglio. Quando un client richiede dei dati, la richiesta passa al controller centrale che instrada verso la Ram che possiede tale informazione. Questa risponde inviando i dati non sullo stesso canale da cui è partita la richiesta e passando nuovamente per il memory controller, ma dall’anello che congiunge tutti i chip di memoria fermandosi in prossimità del ring stop più vicino al client che ne ha fatto richiesta.

L’ampiezza del Ring bus è a 512bit, ma questo non significa che l’ampiezza del memory controller è tale. La differenza sta nel fatto che ora si trasferiscono i dati su 2 bus uniformi nell’ampiezza (256bit) e bi-direzionali (da qui 2x 256bit= 512bit). Per le GPU di fascia inferiore, il ring bus diventa a 256 bit (2x 128bit), quindi è sempre doppio rispetto a quello principale.

I 4 Ring Stop hanno un doppio accesso bidirezionale e a 32bit alla coppia di chip di memoria su cui agiscono.

Anche il memory controller implementa delle funzioni di indirizzamento delle richieste dei client ottimizzabili e programmabili dal driver Catalyst che può dare priorità ora ad un tipo di richiesta ora ad un’altra a seconda dell’applicativo. Inoltre l’interconnessione ad anello permette anche una migliore stabilità dei segnali elettrici potendo raggiungere, quindi, maggiori frequenze di esercizio.

Con lo stesso approccio flessibile, il memory controller può contare su cache non più mappate in maniera diretta o associativa o a N vie, ma pienamente associative, cioè tali per cui ciascuna linea di cache può memorizzare il contenuto di qualsiasi locazione della memoria esterna senza locazioni predefinite e "prenotate". In questo modo la richiesta di banda passante si riduce con un’ottimizzazione che la stessa Ati stima del 25% in alcuni casi, molto vantaggioso con le alte risoluzioni e con i filtri attivi.